【技术 FPGA-3】如何扫描FPGA的IO定义

2025 / 8 / 1

前言

总所周知,垃圾仙人的一大爱好就是捡各种便宜的FPGA板卡,然后逆向扫描其电路IO,然后当作正常开发板来用。如何扫描这类FPGA办卡的各个针脚实际连到FPGA哪个Pin了呢,这就是本文要解决的问题。

准备工作:

1-一块FPGA垃圾板(你确定板子没事吧?

2-这个垃圾板需要完整上电(有些只给5V就够了,常见于各类接收卡;有些12V,常见于各类计算卡;有些甚至VCCIO和VCCINT都要自己给)

3-这个垃圾板需要知道JTAG定义(如果在金手指或者BTB上就难搞了,这个我会出一个暴力扫描的程序来找,小白尽量还是找那种JTAG明确标注的)

4-一台电脑(废话

5-一个可调电平串口(1.2V~3.3V触发电平可调,避免一些低压IO扫不到)

6-一个FTx232H下崽器(驱动比较通用,别的下崽器其实也能用

方法1——使用BSDL

1-工具很多,这里只推荐TOPJTAG(和谐过程略)

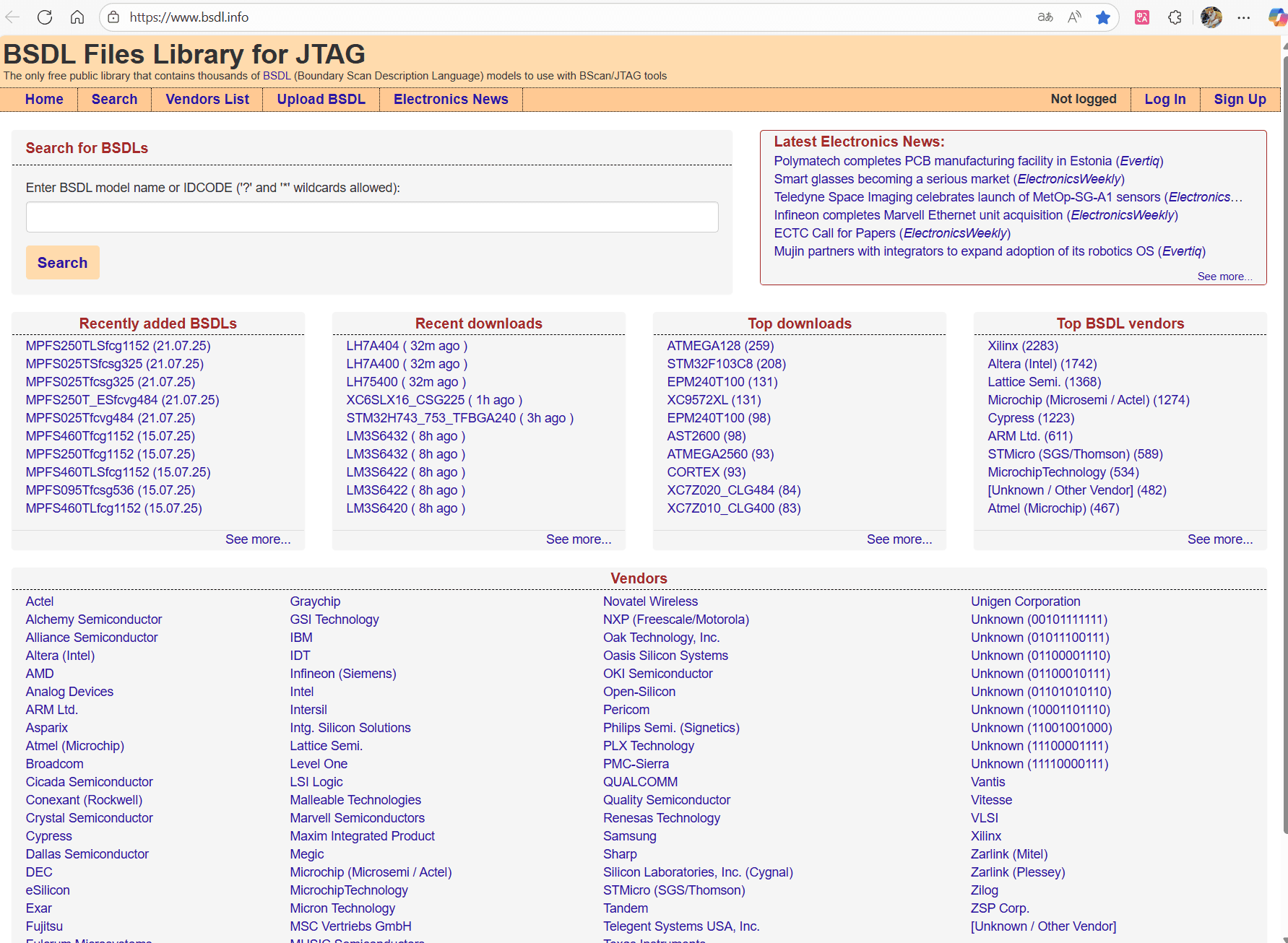

2-去各种网站下载你要测的芯片的BSDL文件,比如这个BSDL Library

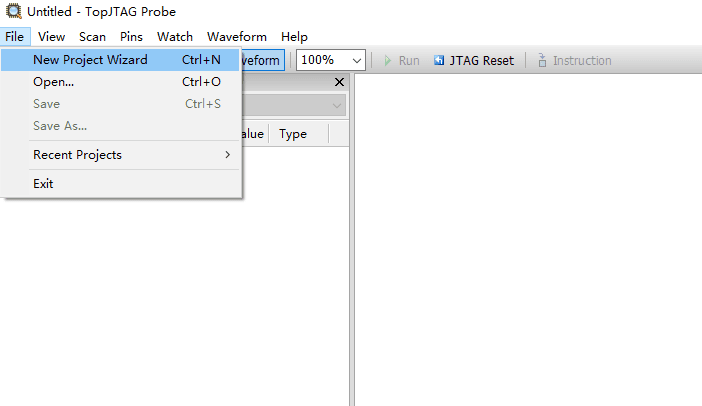

3-打开TOPJTAG,新建一个工程

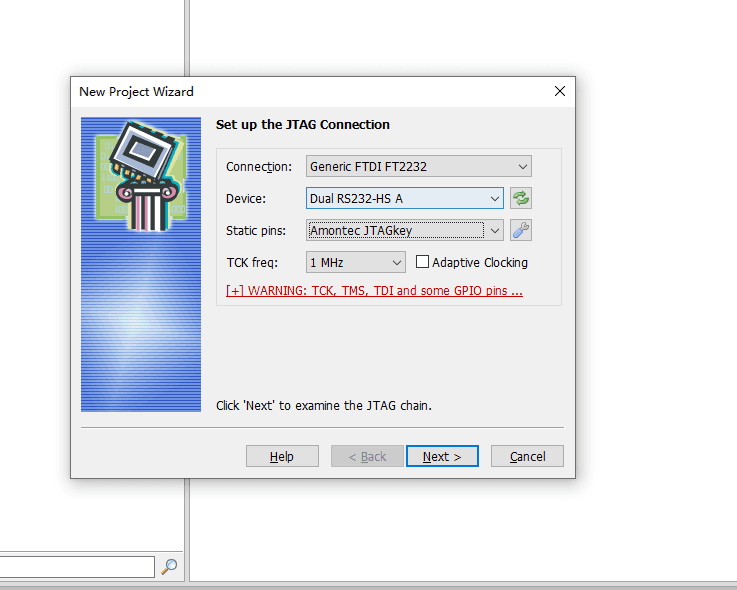

4-选择FT下崽器,A通道(FT2232H的一般都是这个),1Mhz(因为你大概率是杜邦线接的,跑快了认不到)

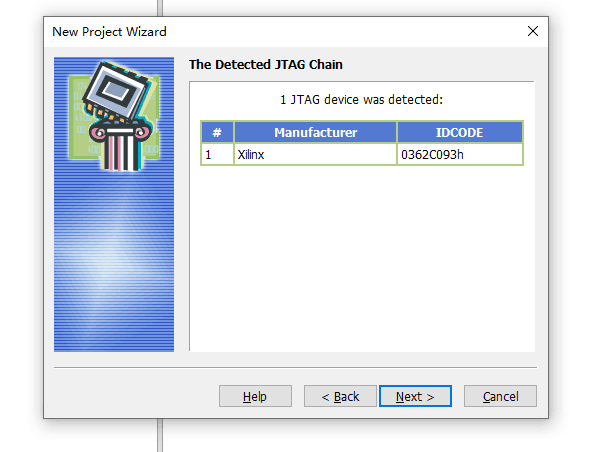

5-Next之后,如果现在插好板子所有连接,应该就认到这个芯片的ID CODE了

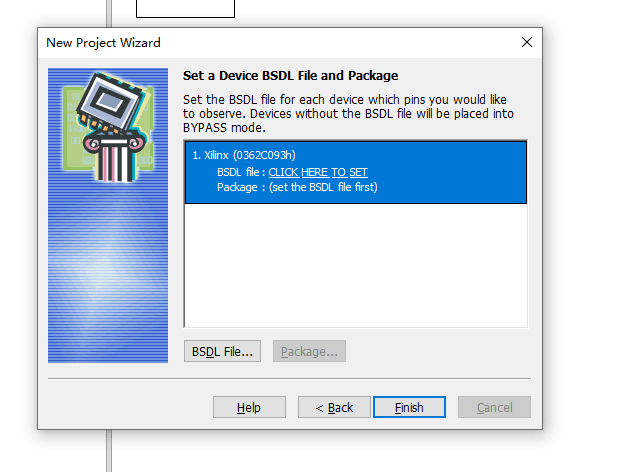

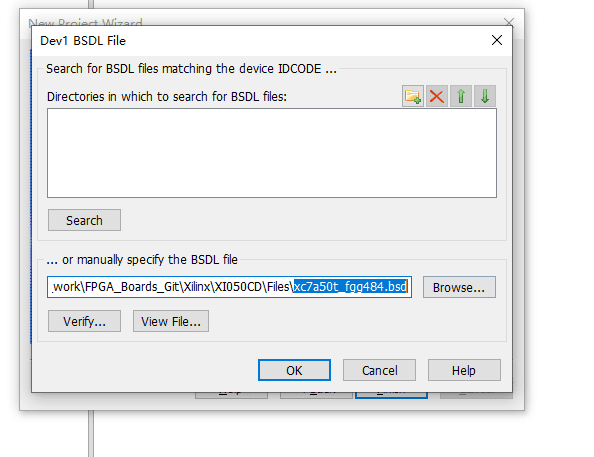

6-Next之后,会要求你选择这个芯片对应的BSDL文件

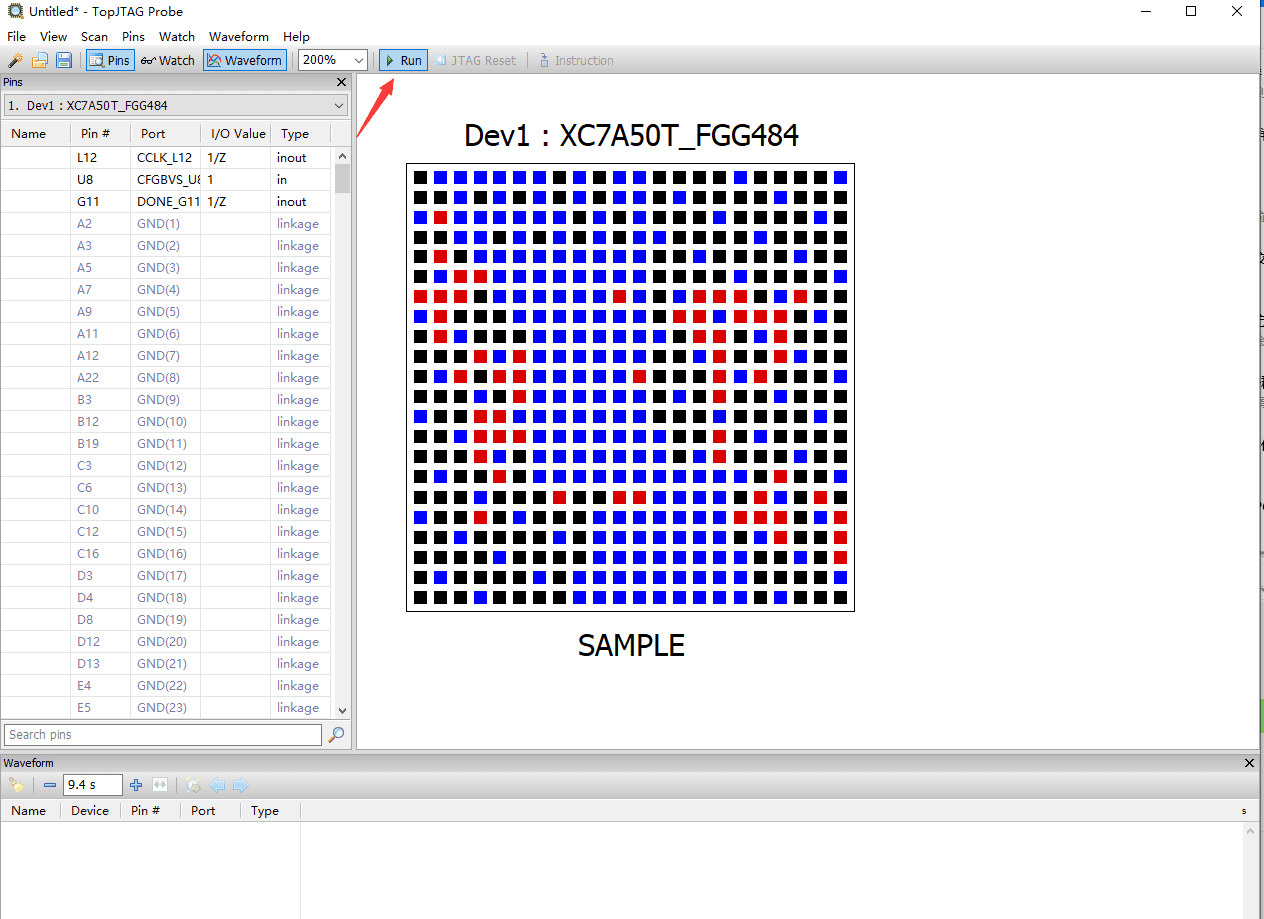

7-选择完成后,点击Run,就会显示FPGA各个IO现在的翻转状态了,你就一个一个去数吧,引脚 0 1翻转的时候会显示为红黑不同颜色

方法2——使用蹄子哥妙妙屋的神奇小工具

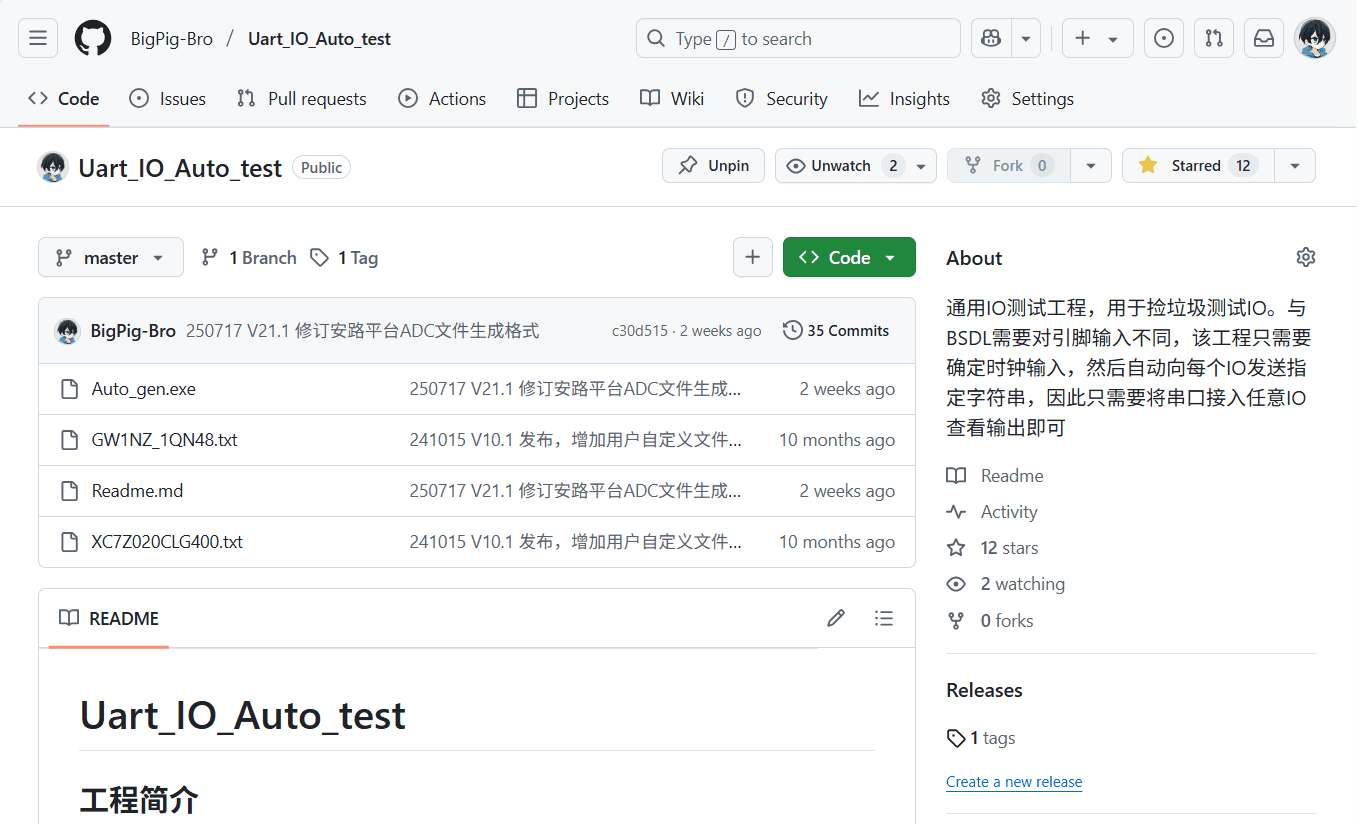

1-首先,你需要去Gayhub下载exe

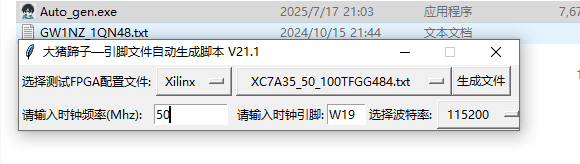

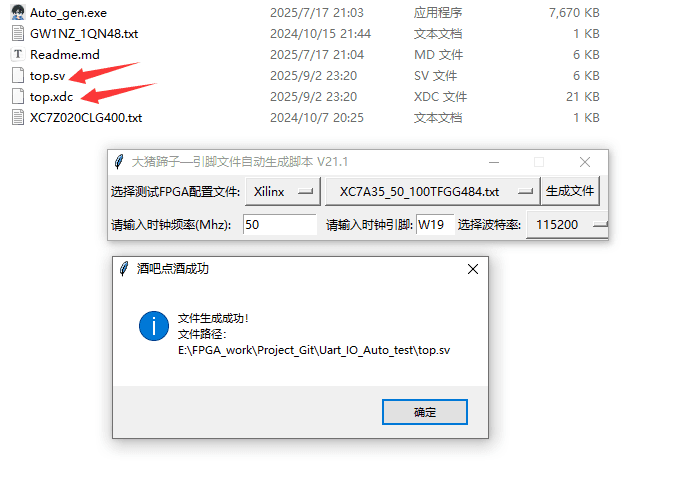

2-打开后选择指定的芯片型号,输入CLK_PIN,频率,串口波特率

3-这个CLK_PIN你可以通过BSDL去扫描(断掉FLASH启动,再看哪些IO在闪),也可以用FPGA内部原语CLK(误差较大,建议使用9600波特率避免误码)

4-生成sv文件和对应约束文件

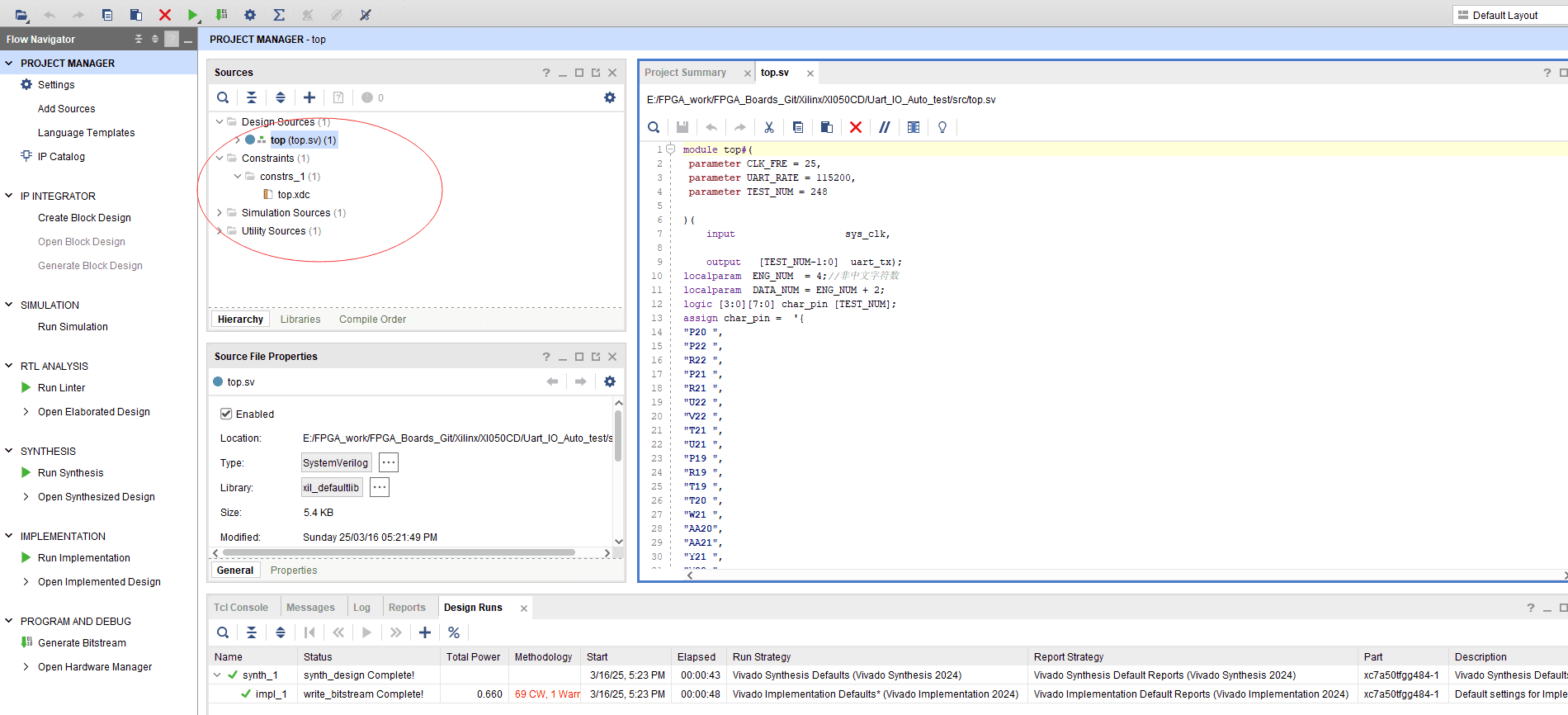

5-创建对应芯片的空工程,把这俩扔进去(有些工程约束文件不是xdc那种独立的,比如Quartus生成的实际上是tcl指令,跑一遍就约上了)

6-编译后下载,然后串口工具和开发板共地,打开电脑串口显示,用串口的RXD去戳任意你觉得是PIN的针脚

7-如果这个PIN连到FPGA IO了,你会在电脑端看到对应的字符输出,比如“AB21”这样

8-然后就是枯燥无聊的划拉一遍了

注意

1-部分PIN是无法通过这些方法测量的,比如电源、GND、GT等等,详细注意事项见Uart_IO_Auto_Test的README.md

2-部分神经板卡把FPGA IO拉到CLK的RST\EN上了,这样会导致测试到这个Pin的时候把CLK掐断了卡住了,常见于各类LED接收卡,有源晶振都要省~,这种卡建议先用原语CLK,然后把RST单独踢出来

版本更新

250801:初始版本